3DS DIMM

В некоторых, очень отдельных областях применения вычислительной техники, памяти много не бывает. За любые деньги, но чтобы все (ну, или — большая часть) в памяти и моментально доступно! Так как скорость обращения к внешней памяти, какой бы быстрой она ни была, существенно ниже, чем скорость работы с внутренней, ряд приложений не может терять время на ожидания — потеря производительности дорого обходится. Но всему есть пределы, обусловленные как принятыми и стандартизованными спецификациями на интерфейс, протокол, и т.д., с одной стороны, так и принятыми конструктивными особенностями реальных комплектующих вычислительной техники — с другой. К примеру, максимальное количество поддерживаемых одним процессором модулей памяти, равно произведению числа каналов памяти на максимальное число модулей на одном канале. Обе цифры жестко ограничены возможностями центрального процессора. Больше каналов особенно не наделаешь. В серии процессоров Scalable, Intel увеличил с 3 до 4 число каналов работы с памятью, но при этом уменьшил число модулей в канале. Каждый из модулей вместе с линией передачи к нему ухудшает характеристики канала, вынуждая снижать скорость передачи данных. Умножаем полученное число на объем одного модуля и получаем максимальный объем оперативной памяти, который может быть подключен на один процессор. Что делать, если полученного объема мало?

Расширение не в плоскости, а по вертикали открывает новые горизонты. Легко увеличить емкость одного модуля динамической памяти путем напайки дополнительных чипов или увеличением емкости чипа за счет его площади не получается. Решили пойти другим путем. А что — если упаковать чипы памяти в несколько «этажей», но внутри одного корпуса?

Существенные доработки

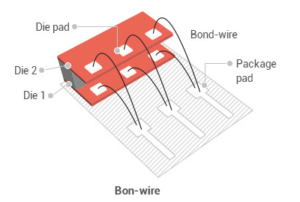

Пришлось попутно решить несколько задач. Первая — собственно, многослойная упаковка. Полупроводниковый чип имеет контактные площадки для соединения с контактными площадками корпуса проволочными проводниками. Соответственно, накладываемый сверху чип необходимо располагать с прослойкой, чтобы иметь доступ к площадкам предыдущего слоя, да еще и распаять, не нарушив уже сформированные. Сложно и нетехнологично.

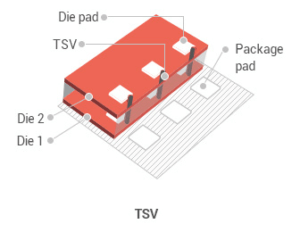

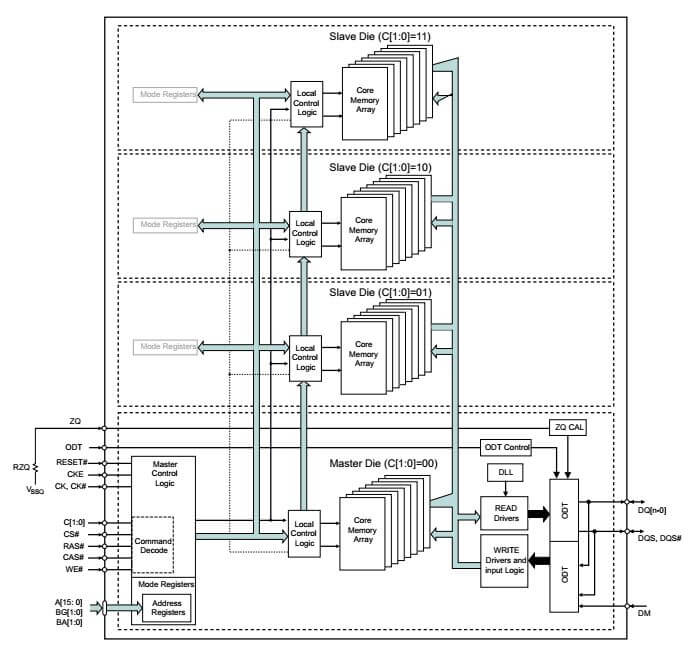

Вторая задача — разгрузка шины. Каждый наслаиваемый чип, непосредственно соединенный с шиной интерфейса ухудшает ее характеристики за счет привнесения паразитных емкостей и увеличения электрической нагрузки. Значит, необходима развязка. Остановились на следующей схеме: первый слой, «мастер», контактирует непосредственно с шиной интерфейса и имеет дополнительную логику-селектор для адресации к различным слоям. Последующие слои, «ведомые», соединяются с только с первым слоем и несколько отличаются схематически, поскольку этой дополнительной логики не имеют. А соединения между слоями осуществляются через сквозные проводники (through-silicon via, TSV).

Что мы имеем в итоге? Или более емкие модули динамической памяти без увеличения емкости чипов, или тот же объем модуля, но на менее емких (значит — более дешевых) чипах памяти. 3DS упаковка затрагивает только компоновку кремниевых чипов в корпус, соответственно — модуль DIMM так же может быть построен с использованием дополнительных буферов для снижения нагрузки (Load Reduced).

Сравнение 3DS LRDIMM с обычной DDP LRDIMM

Потребление энергии

Так как в 3DS модулях используется тот же тип чипов, что и в обычных DDR DIMM, существенной разницы в потреблении энергии между 3DS и не-3DS модулями одинаковой емкости нет.

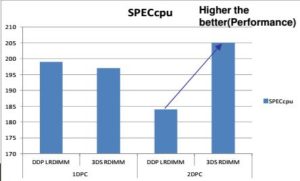

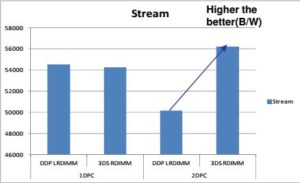

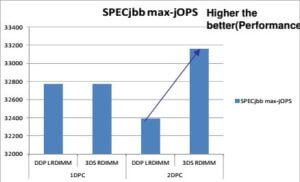

Производительность

С производительностью картина неочевидная. В конфигурации с одним модулем на канал (1DPC, DIMM per channel), производительность 3DS памяти схожа с обычной, небольшое отставание наблюдается за за счет бОльшего числа рефреш циклов, необходимых модулю. Но в конфигурации с двумя модулями на один канал ( 2DPC) ситуация меняется кардинально — если обычная память «проседает» почти на 50%, 3DS память, наоборот — выигрывает от 20 до 50% по разным тестам. Объясняется это меньшим суммарным временем задержки от большего числа ранков. Графики результатов ниже.

Совместимость

3DS модули не совместимы с другими типами памяти. То есть, на одном канале нельзя устанавливать модули разных типов.

Производители

О готовности производить 3DS модули объявили все ведущие игроки в области памяти

SK Hynix

Заявил о «первом в мире» модуле 128GB 3DS LRDIMM с технологией упаковки TSV. Модуль строится на 8ГБ чипах, упакованных в 4 этажа.

| Тип | Технологи-ческие нормы | Базовая емкость чипа | Количество слоев | Емкость модуля | Шина данных | Скорость | Напряжение питания |

|---|---|---|---|---|---|---|---|

| DDR4 | 2ynm | 8Gb | TSV 4Hi | 128GB | x72 | 2400 | 1.2V |

Samsung

Объявил о массовом выпуске 64ГБ 3D TSV DDR4 DRAM в далеком 2014, а 128ГБ модули был готов массово выпускать в ноябре 2015 года.

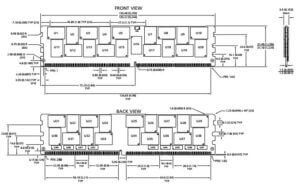

128 ГБ TSV DDR4 RDIMM состоит из 144 чипов DDR4, расположенных в 36 4-гигабайтных пакетах DRAM, каждый из которых содержит четыре 8-гигабитных (Gb) микросхемы, произведенной по нормам 20-нанометров (нм), собранные с использованием передовой технологии упаковки TSV.

Micron

Базовая модель: MT40A8G4 32Gb DDR4 4H 3DS M/S DRAM. 4-слойная упаковка, емкость модуля 128ГБ, Load Reduced.

| Device configuration | 32Gb (128 Meg x 4 x 16 banks x4 ranks) |

| Part Number | Емкость модуля | Конфигурация | Производи-тельность | Скорость | Циклы (CL-tRCD-tRP) |

| MTA144ASQ16G72LSZ-2S6__ | 128GB | 16 Gig x 72 | 21.3 GB/s | 0.75ns/2666 MT/s | 22-19-19 |

| MTA144ASQ16G72LSZ-2S3__ | 128GB | 16 Gig x 72 | 19.2 GB/s | 0.83ns/2400 MT/s | 20-18-18 |

Производители систем

Готовность к использованию 3DS LRDIMM подтверждена (документ) компанией Supermicro в серии серверных материнских плат X11 под процессоры Intel Scalable (LGA3647). Краткое содержание — использовать в платах X11 можно, миксовать в одном канале 3DS LRDIMM с другими типами нельзя.

Перейдите в раздел каталога Серверы для выбора базовой модели и конфигурации готового сервера.

Далее идут технические подробности, которые не всем интересны.

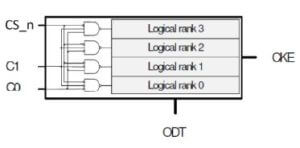

Выбор слоя («этажа»), который в многоэтажной сборке называется «логическим ранком» происходит в селекторе мастер-чипа по сигналам линии шины CS_n, C1, C0.

CS_n показывает — к какому из слоев идет обращение — мастер или слейв

C0, C1 формируют адрес логического ранка. 2 линии адреса позволяют обращаться к 4 подчиненным слоям.

Блок-схема сборки, состоящей из мастер-чипа и 3 подчиненных слоев выглядит так:

На мастер-слой добавлены блоки Master Control Logic, содержащий декодер команд и селектор слоя и общие для сборки буферы и блок ODT Control.

Источники: JDEC, SK Hynix, Micron, Samsung, Techpowerup